2.39.1 ECC 支持概述(Overview of ECC Support)

1. ECC 支持的配置要求

- MEMC_ECC_SUPPORT 参数必须设置为

1,才能启用 ECC 功能。 - MEMC_SIDEBAND_ECC 参数也必须设置为

1。 - 如果 MEMC_SIDEBAND_ECC = 1 和 MEMC_INLINE_ECC = 1,则此节描述的是 Sideband ECC 模式,该模式由

ECCCFG0.ecc_type配置选择。

2. ECC Lane 的定义

- ECC Lane 被定义为一个数据字(word),其宽度等于 SDRAM 宽度,ECC 计算在这些数据字上进行。

- DFI 接口(DDR接口)每个时钟周期传输两个或四个 ECC lane 数据,具体数量取决于控制器的频率配置 MEMC_FREQ_RATIO。

3. 支持的 ECC 类型:SEC/DED(单比特单错误校正 / 双比特检测错误)

控制器支持 SEC/DED ECC,这是 Single Bit Single Error Correction / Double Error Detection(单比特单错误校正 / 双比特错误检测)。

支持的配置包括:

- SDRAM 数据宽度:16、32 或 64 位。

- MEMC_DRAM_DATA_WIDTH:必须设置为 16、32 或 64。

支持的内存宽度:控制器支持 16 位、32 位和 64 位数据宽度的 ECC 校验。如果配置为其他宽度(如 8 位),则不支持 ECC。

4. ECC 支持的内存类型

- ECC 支持所有 DDR 协议,但对于 mDDR、LPDDR3 和 LPDDR4,其最小设备宽度为 16 位。

- 对于 LPDDR3/4,ECC 不一定在所有 PHY(物理层)上都得到支持,因为 PHY 可能要求总数据宽度为 16 的倍数。

2.39.2 配置和基本操作(Configuration and Basic Operation)

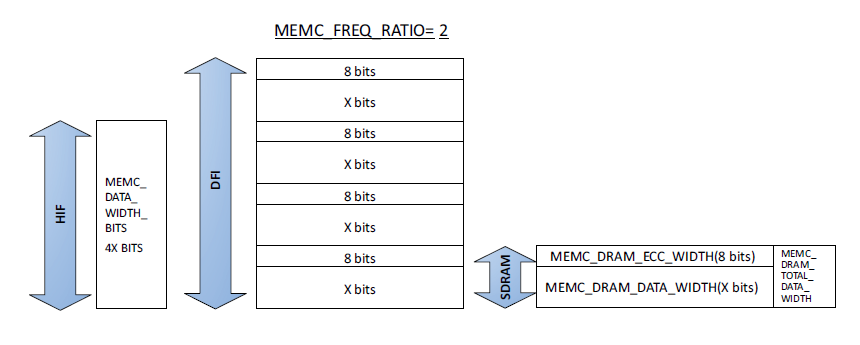

1. 数据位宽的变化

- MEMC_ECC_SUPPORT = 1 和 MEMC_SIDEBAND_ECC = 1 会扩展 DFI(DDR 接口)数据位宽,以容纳额外的 ECC 字节。

- 每个 ECC lane 会增加一个 ECC 字节。

- 在 1:1 配置模式(MEMC_FREQ_RATIO = 1)中,假设 SDRAM 宽度 为 64 位(MEMC_DRAM_DATA_WIDTH = 64),则 DFI 数据宽度从 128 位增加到 144 位。

- 在 1:2 配置模式(MEMC_FREQ_RATIO = 2)中,假设 SDRAM 宽度 为 64 位,DFI 数据宽度从 256 位增加到 288 位。

解释:

- ECC lane:在 ECC 校验中,数据被划分为多个“ECC lane”(数据块),每个 ECC lane 宽度与内存数据宽度相同。

- DFI 数据位宽:在启用 ECC 后,DFI 接口的数据传输宽度会增加,因为需要额外传输每个 ECC lane 的 ECC 校验字节。这个增加的宽度取决于内存配置和频率设置。

- MEMC_FREQ_RATIO:控制器的频率比,决定了数据传输的速率。频率比为 1:1 或 1:2 会影响 DFI 数据位宽的变化。

2. ECC 配置

- 如果控制器已配置为支持 ECC,则通过软件使能寄存器 ECCCFG0.ecc_mode 来启用或禁用 ECC。

- 如果 ECCCFG0.ecc_mode = “100”,则启用 单比特单错误校正 / 双比特错误检测(SEC/DED ECC)模式。

解释:

- ECCCFG0.ecc_mode:该寄存器用于控制是否启用 ECC 校验。如果设置为

100,则启用单比特单错误校正(SEC)和双比特错误检测(DED)。这意味着数据传输时会进行错误校正和错误检测。

3. 写入操作中的 ECC

- 在写入操作时,ECC 会在每个 ECC lane 上计算,并将结果的 ECC 码作为额外的字节与数据一起写入 SDRAM。

- 这个额外的 ECC 字节总是写入 SDRAM 的最高字节位置:对于 16 位 SDRAM 是第 2 字节,对于 32 位 SDRAM 是第 4 字节,对于 64 位 SDRAM 是第 8 字节。

解释:

- 写入数据:在写入数据时,ECC 校验码会与数据一起写入内存。这个 ECC 校验码会覆盖内存中的特定字节,通常是内存地址的最高字节,以确保 ECC 校验能够正确应用。

4. 读取操作中的 ECC

- 在读取操作时,包含 ECC 字节的 ECC lane 会从 SDRAM 中读取,并进行 解码。

- 控制器会验证读取到的 ECC 字节是否正确,即与数据在 ECC lane 中的期望值匹配。如果匹配,数据将被正常发送到系统(SoC)。

- 如果 ECC 校验发现错误,控制器会根据错误的类型(例如单比特错误或双比特错误)采取相应的处理措施(详见“ECC 错误时的控制器行为”部分)。

解释:

- 读取数据:当控制器从内存中读取数据时,除了数据外,还会读取 ECC 校验字节。然后控制器会检查该 ECC 校验字节是否与数据一致,以确认数据是否在传输过程中没有出错。如果 ECC 校验通过,数据就可以正常返回给系统。如果检测到错误,系统会根据设定的错误处理机制进行处理。

5. 读修改写(RMW)操作中的 ECC

- 在 读修改写 操作中,首先会执行读取操作,如前所述,读取的数据和 ECC 校验字节。

- 然后,读取的数据与从 HIF(主机接口) 接收到的写数据合并,使用 HIF 提供的写掩码来覆盖读取数据中的特定字节。

- 对于合并后的数据,控制器会重新计算 ECC 校验,并将其写回内存。

解释:

- 读修改写(RMW)操作:这种操作涉及先读取数据,再对数据进行修改并写回内存。在执行 RMW 时,控制器需要首先读取数据并进行 ECC 校验。然后,新的数据与原有数据合并,ECC 校验码会基于更新后的数据重新计算,并与数据一起写回内存。

2.39.3 全总线宽/半总线宽/四分总线宽模式(Full / Half / Quarter Bus Width Mode)

1. ECC 的计算和解码

- 在 ECC 引擎 中计算和解码的数据会通过 DQ 总线的单边传输(单边指数据仅在 DQ 总线的一个时钟边缘进行传输)。

- 当 MEMC_DRAM_DATA_WIDTH = 64 时,如果输入到 ECC 引擎的数据宽度小于 64 位,控制器会填充零(padding zeros)使其对齐为 64 位数据,之后再传送到 ECC 引擎进行编码或解码。

解释:

- ECC 引擎:用于执行错误校正和错误检测的硬件单元。

- MEMC_DRAM_DATA_WIDTH = 64:表示内存的数据总线宽度为 64 位。

- 填充零(padding zeros):如果输入数据宽度小于 64 位,控制器会在数据中添加零,确保数据总宽度为 64 位,从而能够与内存总线对齐进行传输。

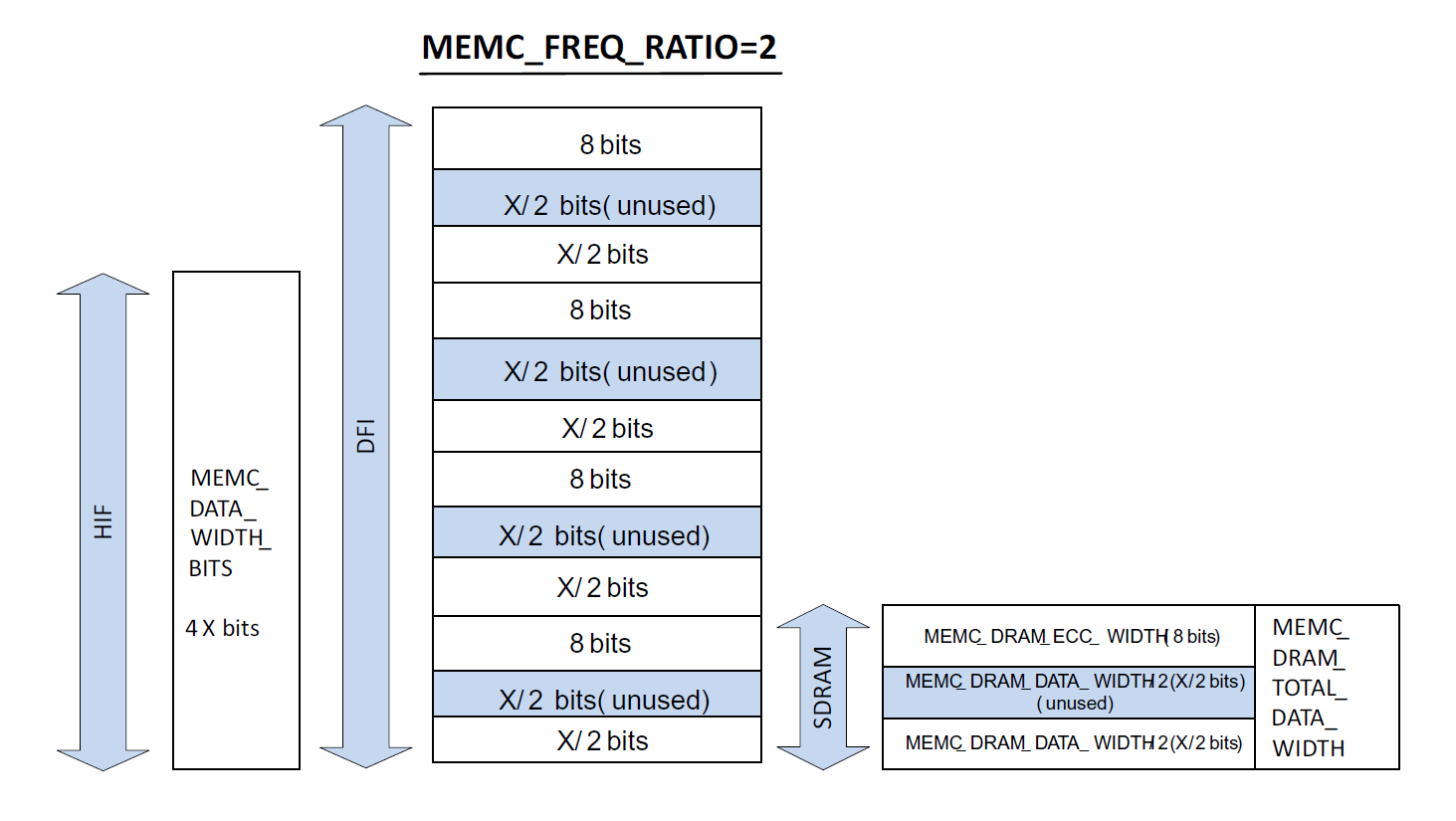

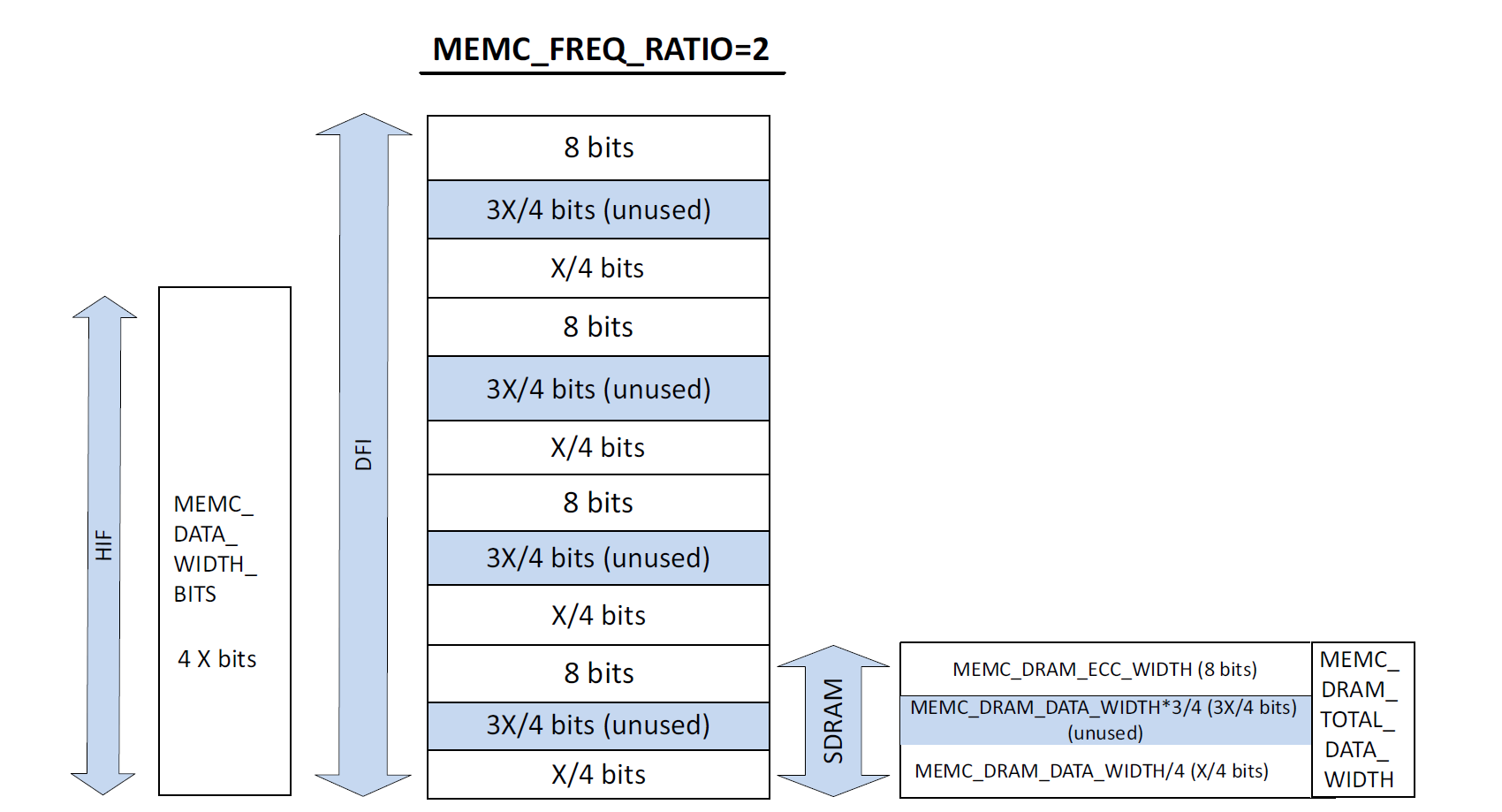

2. 半总线宽和四分总线宽的处理

- 在 半总线宽模式(HBW)或 四分总线宽模式(QBW)下,数据在 ECC 编码阶段 会被拆分成多个周期进行处理。

- 数据会被分割成多个周期,并根据需要添加填充位(padding),然后送入 ECC 引擎 进行编码。

- 在解码阶段,从 PHY(物理层接口)接收到的数据会送入 ECC 解码器,并根据需要进行填充。

- 在 半总线宽模式(HBW)和 四分总线宽模式(QBW)下,数据的收集是在数据通过 ECC 解码器 之后进行的。

解释:

- 半总线宽模式(HBW) 和 四分总线宽模式(QBW):这两种模式下,内存的数据总线宽度会小于 64 位(可能是 32 位或 16 位)。为了能够进行 ECC 校验,控制器会将数据分割成多个小周期进行处理。

- 编码和解码阶段:在编码阶段,数据被拆分成多个周期并进行填充,然后传送给 ECC 引擎;在解码阶段,数据会经过 ECC 解码器,并根据需要填充,确保数据完整性。

3. ECC 字节的位置

- 在启用 ECC 的 半总线宽模式(HBW)或 四分总线宽模式(QBW)下,ECC 字节总是会被写入到 SDRAM 接口的最显著字节(最高字节),以及 DFI 接口的每一个阶段。

- HBW 和 QBW 模式下,ECC 字节总是写入到最显著字节,确保数据的 ECC 校验可以在传输过程中正确应用。

解释:

- 最显著字节(Most Significant Byte):在多字节数据中,最显著字节是数据中值最大的字节,即数字中位数最高的部分。在内存存储中,ECC 校验通常存储在这些字节中,以便在出现错误时进行检测和修复。

- DFI 接口:即 DDR 接口,控制器和内存之间的数据传输通道。

- ECC 字节的存储:无论是 HBW 还是 QBW 模式,ECC 字节都会被存储在内存的最高字节,确保 ECC 校验覆盖整个数据。

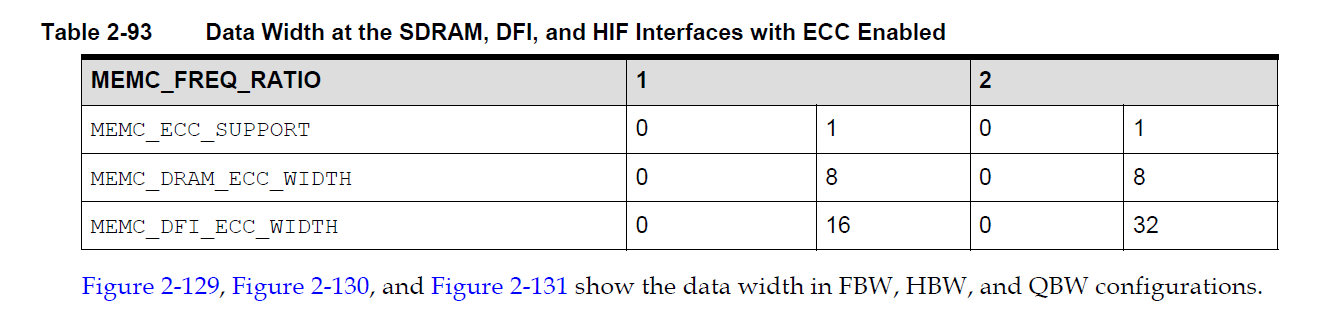

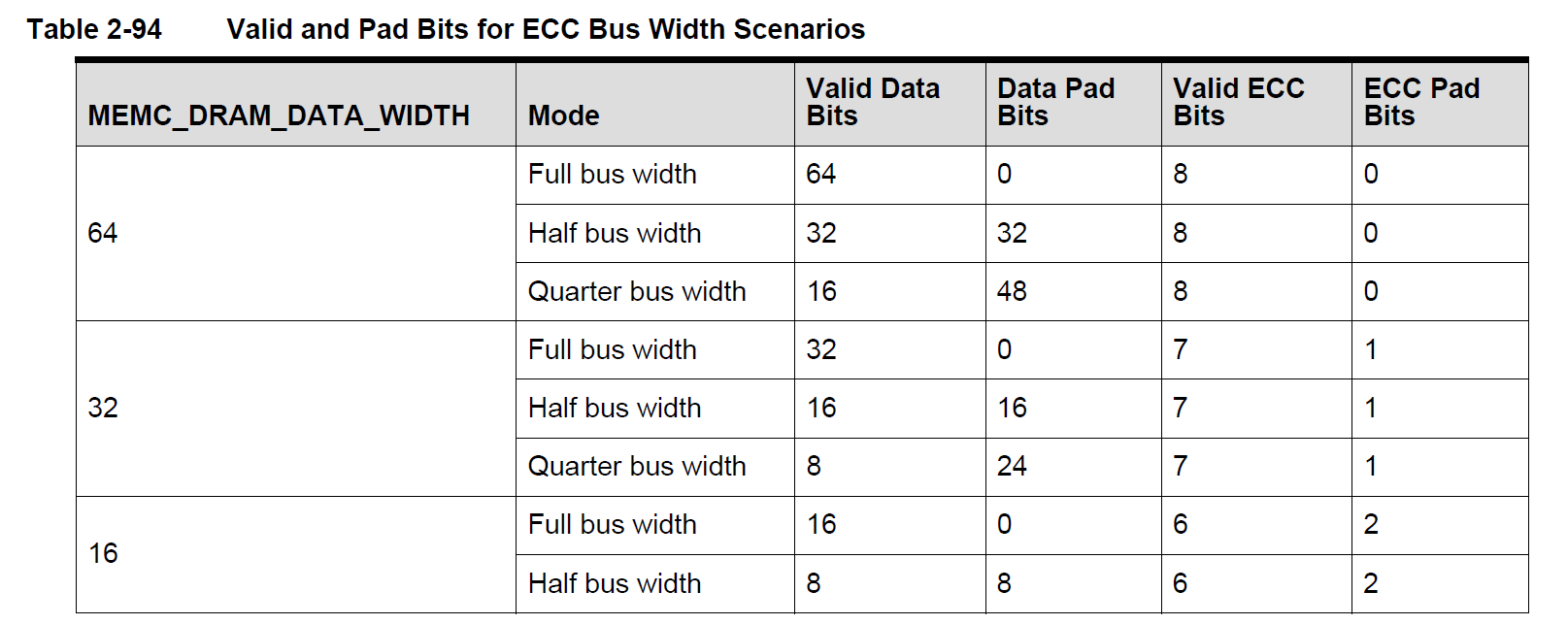

4. 表格和数据宽度

- 手册中提到的表格(表 2-93)显示了在不同总线宽模式下,ECC 字节和 填充字节 的数量。

解释:

- 表格提供了在不同模式下,ECC 字节和填充字节的具体数量,帮助开发者理解在不同配置下 ECC 校验和数据传输的实际宽度。

2.39.4 使用 ECC 时的数据掩码限制

1. ECC 操作与写操作粒度

- 每个 ECC lane(ECC 处理的数据通道)的宽度可以是 16 位、32 位或 64 位。如果启用 ECC 功能,uMCTL2 控制器 会根据写操作的数据粒度(即写入的数据字节数)来判断如何进行写操作。

- 写操作粒度要求:

- 如果写入数据的字节数是 2 字节、4 字节或 8 字节对齐的,控制器可以直接执行写操作。

- 如果写入数据的字节数小于 2 字节、4 字节或 8 字节对齐的(即不是按照这些字节数对齐),控制器会执行一个 RMW(Read-Modify-Write)操作。

2. RMW 操作的处理方式

- 在 RMW 操作中,控制器会首先从 DRAM 读取当前的数据,之后将从控制器传送来的写数据与已读数据合并,再写回内存。

- 在进行 RMW 操作时,控制器会执行 无掩码写入,意味着没有对数据字节进行掩码(即不跳过任何字节,所有字节都会被写入)。这避免了由于数据掩码造成的潜在错误。

总结:当数据粒度不满足对齐要求时,控制器会通过读取当前内存中的数据并与写入的数据合并,进行 RMW 操作,以确保数据的一致性。

2.39.5 ECC 错误处理机制

1. 可纠正的 ECC 错误

当 uMCTL2 检测到一个 可纠正的 ECC 错误 时,控制器会执行以下操作:

- 将 已修正的数据 作为读数据返回给 SoC。

- 将 ECC 错误信息 发送到 APB 寄存器模块。

- 执行 RMW 操作,修正存在于 SDRAM 中的错误数据(只有在启用 ECC 清理功能时,ECCCFG0.dis_scrub = 0)。该 RMW 操作对于控制器是 透明的,即控制器不会感知到这个操作的具体细节。

总结:当可纠正的 ECC 错误被检测到时,控制器会先修正数据并将修正后的数据发送给 SoC,随后对 SDRAM 中的错误数据进行修复。

2. 不可纠正的 ECC 错误

当控制器检测到一个 不可纠正的 ECC 错误 时,执行以下操作:

- 将 出错的数据 作为读数据发送给 SoC。

- 将 ECC 错误信息 发送到 APB 寄存器模块。

- 生成一个错误响应,在 AHB 接口 或 AXI 接口 上生成 SLVERR 响应。

3. RMW 操作中的不可纠正错误处理

如果在正常的 RMW 操作的 读部分(而非 ECC 清理操作)中检测到不可纠正的错误,控制器将:

- 在随后的写操作部分,故意 破坏 2 位(2-bit corruption)到重新计算的 ECC 字段中。

- 这种故意破坏的操作确保了 不会发生自动修复,避免了由于 ECC 校验失败的错误数据被误修正。

总结:对于不可纠正的 ECC 错误,控制器不会修复数据,而是将错误数据发送给 SoC,并确保没有因自动 ECC 修复机制而错误地修正这些错误。

4. ECC 错误的报告

- ECC 错误报告基于 DFI 读数据。对于小而不对齐的 AXI 事务,可能有部分数据不会传播到 AXI 接口,但即使这些数据没有使用,ECC 错误仍会被标记。特别是对于未初始化的内存区域,可能会发生这种情况。

- 为了避免此类错误,推荐在初始化时将整个内存空间进行初始化。

总结:ECC 错误报告会基于整个 DFI 读数据进行,确保即使是未使用的部分数据也能标记 ECC 错误。为了避免未初始化内存导致的问题,建议在初始化时对内存进行完全初始化。

2.39.5.1 ECC 错误报告寄存器

- 控制器提供了一系列的寄存器,用于 ECC 错误报告。通过读取这些寄存器,可以获得关于已检测错误的详细信息。

- 控制器还提供了 两个中断:

ecc_corrected_err_intr和ecc_uncorrected_err_intr,当检测到纠正或未纠正的错误时,这些中断会被触发。 - ECC 错误日志寄存器 用于捕捉 第一次 ECC 可纠正错误 和 第一次 ECC 不可纠正错误,并存储相关的日志信息,直到相关中断被清除。

2.39.5.1.1 ECCSTAT.corrected_bit_num 字段

ECCSTAT是一个寄存器,它用于保存 ECC 错误的状态信息。当 ECC 错误被检测到时,这个寄存器会记录有关错误的详细信息。- 在

ECCSTAT中,corrected_bit_num是一个字段,用来表示已经被修正的 ECC 错误位。这个字段的值指示了在 ECC 检测到错误后,具体是哪个位出现了错误并被修正。(详细看表)

2.39.6 ECC Scrub(ECC 清理)和 ECC Scrubber(ECC 清理器)

在 DRAM 操作中,错误是不可避免的,尤其是单比特错误,这些错误通常是由环境因素(如辐射)引起的。ECC Scrub 和 ECC Scrubber 的目标是定期修复这些单比特错误,以防止它们演变成更严重的不可修复的错误(如双比特错误)。

1. ECC Scrub 特性

- ECC Scrub 是一种自动修正机制,用于修复 DRAM 中的单比特错误。它可以在读取时触发修复过程。

- 启用 ECC Scrub 需要满足以下条件:

MEMC_USE_RMW = 1:必须启用 RMW(读取-修改-写入)操作。MEMC_ECC_SUPPORT > 0:必须启用 ECC 支持。

- 在 ECC Scrub 启用时,任何接收到的 读取命令,如果发现其中包含单比特错误,将触发自动 ECC Scrub 操作,修复这些错误。

- ECC Scrub 的启用和禁用:

- 通过设置

ECCCFG0.dis_scrub = 0来启用 ECC Scrub,此参数与 ECC Scrubber 是否启用无关。 - 如果使用 Sideband ECC 配置(即

MEMC_ECC_SUPPORT > 0且MEMC_SIDEBAND_ECC == 1),则可以通过将ECCCFG0.dis_scrub = 0来启用 ECC Scrub。 - 在 Inline ECC 配置下(即

MEMC_ECC_SUPPORT > 0且MEMC_INLINE_ECC == 1),ECC Scrub 功能不可用,始终通过ECCCFG0.dis_scrub = 1禁用。但如果同时设置了MEMC_INLINE_ECC == 1和MEMC_SIDEBAND_ECC == 1,且ECCCFG0.ecc_type = 0时,ECC Scrub 可以在软件禁用 Inline ECC 时启用。

- 通过设置

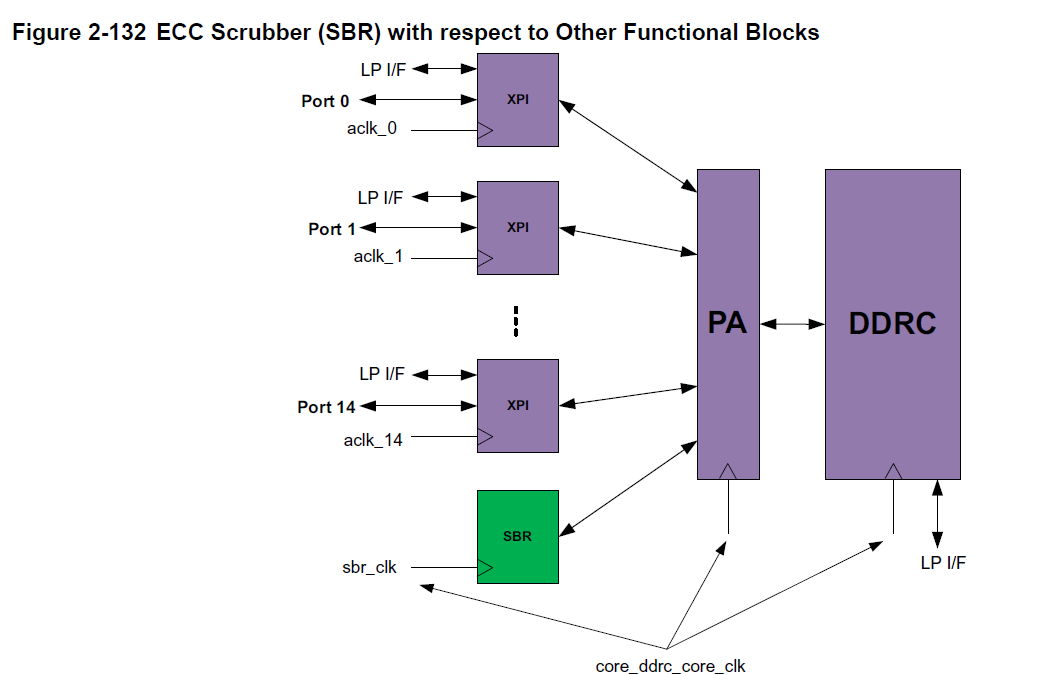

2. ECC Scrubber(清理器)

- ECC Scrubber 是一个外部于 DDR 控制器的硬件模块,它可以定期生成后台读取命令。这些命令的目的是在单比特错误成为不可修复的双比特错误之前,及时纠正这些单比特错误,从而提高系统的可靠性。

- 启用 ECC Scrubber 需要以下硬件参数设置为

1:UMCTL2_SBR_EN:启用 ECC Scrubber。UMCTL2_INCL_ARB:包括在内的仲裁。MEMC_USE_RMW:启用读取-修改-写入操作。MEMC_ECC_SUPPORT > 0:启用 ECC 支持。

- 在 Inline ECC 模式 下,ECC Scrubber 模块仍会生成定期的后台读取命令,并对导致单比特错误的读取命令执行 ECC Scrub 操作。

2.39.6.1 ECC Scrub 功能概述

ECC Scrub 是 DDR 控制器中的一项功能,旨在自动修复 DRAM 中的单比特错误。当检测到单比特错误时,ECC Scrub 会通过 读取-修改-写入(RMW) 操作来修正这个错误。这个功能仅在启用了 Sideband ECC 配置时有效。

1. Sideband ECC 配置

- Sideband ECC 是一种错误检测机制,它将 ECC 校验信息通过额外的通道(sideband)传输给控制器,而不直接嵌入到数据流中。只有在 Sideband ECC 配置下,ECC Scrub 功能才会被启用。

- 配置要求:

MEMC_ECC_SUPPORT > 0:必须启用 ECC 支持。MEMC_SIDEBAND_ECC == 1:启用 Sideband ECC。MEMC_USE_RMW == 1:启用读取-修改-写入(RMW)操作。

2. 启用和禁用 ECC Scrub

- 通过设置

ECCCFG0.dis_scrub = 0来启用 ECC Scrub 功能,dis_scrub是一个控制寄存器字段。当这个字段被设置为0时,表示启用 ECC Scrub。 - 通过将

ECCCFG0.dis_scrub设置为1可以禁用此功能。

3. ECC Scrub 操作流程

- 检测到单比特错误时:

- 当 ECC 解码器 检测到一个单比特错误时,uMCTL2 控制器会调度一个 ECC Scrub 操作。

- 这个操作会作为一个新的 RMW 操作被执行,作用于检测到单比特错误的地址。

- RMW 操作的执行:

- ECC Scrub 是通过 读取-修改-写入(RMW)操作来进行修复的。首先,控制器会发出一个读取请求,读取出错误数据。接着,错误数据会被 ECC 解码器修正,然后将修正后的数据写入到正确的地址。

- 在执行 ECC Scrub 时,读取 操作必须在 写入 操作之前完成。这个顺序是为了确保读取的数据已经经过 ECC 解码器修正,再写入到适当的存储位置。

4. CAM(Content Addressable Memory)条目

- 在 ECC Scrub 操作中,读取 和 写入 CAM 各有一个条目被保留,用于存储 ECC Scrub 请求的地址。

- 每次当检测到单比特错误时,uMCTL2 会从 CAM 中分配一个 读取 和一个 写入 条目,用于执行 ECC Scrub 操作。

5. 关于单一 ECC Scrub 操作

- 限制: 在 uMCTL2 中,任何时候只能有一个 ECC Scrub 操作。这意味着当一个 ECC Scrub 操作 正在执行时,系统不会响应其他单比特错误,直到当前的 Scrub 操作完成。

- 何时完成: 当写入 CAM 条目被释放后,表示当前的 Scrub 操作完成。这时,系统才能开始处理新的 Scrub 请求。

6. 在 Inline ECC 模式下的行为

- 如果 Inline ECC 模式启用(即

MEMC_INLINE_ECC == 1),ECC Scrub 功能不可用。无论MEMC_SIDEBAND_ECC是否设置为1,都不会启用 ECC Scrub。 - 在 Inline ECC 模式 下,

ECCCFG0.dis_scrub必须设置为1,并且系统不会自动进行每次可修正的读取错误的清理(scrubbing)。

2.39.6.2 ECC Scrubber

1. 背景读取命令

ECC Scrubber模块周期性地向DDR控制器发出读取命令,这些命令用于检查内存中的错误。这些命令的优先级很低,因此它们不会干扰正常的内存操作。

2. 读取内存突发

“Scrub命令”实际上是对一个内存突发的读取(例如,BL8),并定期以最低优先级发送到DDR控制器(DDRC)。这些命令的作用是“擦除”内存中的潜在错误,确保内存的可靠性。

3. SBR时钟和复位

ECC Scrubber模块有自己独立的时钟(sbr_clk)和复位信号(sbr_resetn),与DDR控制器的主时钟(core_ddrc_core_clk)和复位信号(core_ddrc_rstn)是分开的。然而,这些信号必须是同步的,即它们必须保持相同的频率并同步运行。

4. 低功耗下的工作

即使DDR控制器的时钟被关闭或进入低功耗模式,SBR模块仍然能够继续工作,执行计数和发出退出低功耗的请求。这是因为SBR模块具有独立的时钟控制。

ECC Scrubber与控制器的关系

- ECC Scrubber模块使用端口仲裁器(Port Arbiter,PA)中的一个端口作为请求者。PA会根据需要分配资源。

- 如果SBR被启用,最多支持15个应用端口,而不是16个。

自动化灵活的擦除方案

- 错误检测和修复

SBR会定期发出擦除读取命令,并在检测到单比特ECC错误时,DDR控制器会自动执行读修改写(Read-Modify-Write,RMW)命令来修复错误。- 只有当启用ECC擦除功能时,DDR控制器才会发出RMW命令。这是通过将

ECCCFG0.dis_scrub设置为0来启用的。 - 如果使用内联ECC模式,则不支持DDR控制器的ECC擦除功能(

ECCCFG0.dis_scrub始终为1)。因此,在这种模式下,SBR模块会检测到每个正确able(可修复)错误并发出RMW命令。

- 只有当启用ECC擦除功能时,DDR控制器才会发出RMW命令。这是通过将

- 只能检测定期读取的错误

SBR只能检测它自己发出的定期读取命令中的可修复错误(如单比特ECC错误)。如果是其他通过AXI总线发出的读取命令,SBR模块无法检测这些错误。 - RMW命令的执行

在SBR检测到正确able的读取错误后,它会发出一个完全屏蔽的(即所有字节禁用的)单个RMW命令。这是为了修复检测到的错误。

Scrub周期和间隔

- Scrub间隔(tSCRUBI)

Scrub间隔定义了两次擦除读取命令之间的时钟周期数。间隔越长,SBR发出擦除命令的频率就越低。 - Scrub周期

Scrub周期是指完成对整个SDRAM地址范围的所有内存位置的读取所需的时间。

通过寄存器SBRCTL.scrub_interval[12:0],可以设置擦除间隔的值。每个间隔的单位是512个sbr_clk时钟周期。- 例如,值为1时,间隔为512个

sbr_clk时钟周期;值为2时,间隔为1024个时钟周期,以此类推。

- 例如,值为1时,间隔为512个

特殊情况:scrub_interval为0时的行为

Scrub Read命令和初始化写命令

当

SBRCTL.scrub_interval的值为0时,表示擦除读取命令(scrub read commands)或者初始化写命令(initialization write commands)会被连续发出。这意味着两个命令之间没有间隔,直接背靠背执行。Inline-ECC模式下的行为

- 如果在内联ECC模式(Inline-ECC mode)下,当

SBRCTL.scrub_interval设置为0时,SBR不会发出任何读修改写(RMW)命令,即使在它的擦除读取命令中检测到单比特ECC错误。 - 内联ECC模式下,ECC错误会通过其他机制进行修复,而不会通过SBR模块的RMW命令进行自动修复。

- 如果在内联ECC模式(Inline-ECC mode)下,当

Sideband-ECC模式下的行为

- 在旁路ECC模式(Sideband-ECC mode)下,如果

SBRCTL.scrub_interval设置为0,当检测到单比特ECC错误时,DDR控制器(DDRC)会发出RMW命令来修复错误。 - 这是ECC Scrubber的一个关键区别:在旁路ECC模式下,SBR会触发DDR控制器进行错误修复,而在内联ECC模式下,则不会。

- 在旁路ECC模式(Sideband-ECC mode)下,如果

tSCRUBI计数器

tSCRUBI计数器的宽度tSCRUBI计数器的宽度为22位,这个计数器用于控制擦除操作的时间间隔。它的宽度由以下几个因素决定:- 9位粒度(x512),意味着每次计数增加512个

sbr_clk时钟周期。 - 最高控制器时钟频率:1066 MHz,最长擦除周期:12小时,最小内存大小:512 Mb DDR3(1个rank)。

- 最低控制器时钟频率:200 MHz,最短擦除周期:2小时,最大内存大小:16 Gb DDR4(4个rank)。

因此,

tSCRUBI的计数器宽度为22位,可以支持从2小时到12小时不等的擦除周期,具体取决于时钟频率、内存大小以及tSCRUBI的配置。- 9位粒度(x512),意味着每次计数增加512个

正常操作

- SBR启用

SBR模块通过设置SBRCTL.scrub_en寄存器启用(具体的寄存器位置请参考手册中的“UMCTL2_MP Registers”章节)。 - Sideband ECC模式下的工作方式

当启用Sideband ECC模式且DDR控制器处于正常工作模式(即内存已初始化并且不在低功耗模式下)时,SBR会周期性地发出擦除命令,且擦除命令的优先级非常低。每个tSCRUBI周期后,会发出一个擦除命令。 - Inline ECC模式下的工作方式

在内联ECC模式下,SBR会发出最少8个突发(burst)命令,这些命令每次都会发到DDR控制器。具体的突发命令数量由SBRCTL.scrub_burst[2:0]寄存器设置。 - 命令队列

每当tSCRUBI计数器到期时,擦除命令(或多个突发命令)会被推送到一个深度为8的队列(scrub queue)。这些命令会立即被发出到DDR控制器。 如果队列中的命令数超过8个(即队列已满),而DDR控制器正忙于执行其他任务,SBR计数器会暂停,直到有空闲的命令槽位。

地址配置

起始地址和最大地址

当ECC Scrubber启用时,擦除命令的起始地址和最大地址可以通过两个寄存器配置:SBRSTART1.sbr_address_start_mask_1和SBRSTART0.sbr_address_start_mask_0:这两个寄存器共同配置SBR的起始地址。SBRRANGE1.sbr_address_range_mask_1和SBRRANGE0.sbr_address_range_mask_0:这两个寄存器共同配置SBR的地址范围。

SBR会根据这些配置,决定在哪个内存地址范围内发出擦除命令。

双通道配置(Dual Channel)下,ECC Scrubber(ECC擦除器)如何管理内存地址和范围

1. 双通道配置下的SBR寄存器

对于双通道配置(Dual Channel Configuration),CH1(通道1)的ECC Scrubber有一组专用的寄存器。它们用于配置和管理SBR(Scrubber)在该通道的地址范围。具体的寄存器如下:

SBRSTART0DCH1.sbr_address_start_mask_dch1_0SBRSTART1DCH1.sbr_address_start_mask_dch1_1SBRRANGE0DCH1.sbr_address_range_mask_dch1_0SBRRANGE1DCH1.sbr_address_range_mask_dch1_1

这些寄存器与通道1的SBR相关,用来设置起始地址和地址范围。

2. 寄存器设置条件

在修改SBR地址寄存器时,有一些条件必须满足:

- 必须在SBR被禁用时修改:这意味着需要将

SBRCTL.scrub_en寄存器设置为0,表示禁用SBR。 - 没有正在进行的擦除命令:

SBRSTAT.scrub_busy寄存器需要是0,即没有正在执行的SBR命令。

只有在这些条件满足的情况下,才能安全地更改地址相关的寄存器。

3. Sideband ECC模式下的寄存器设置

正常模式下的默认值

在Sideband ECC模式下,如果使用正常操作模式(Non-Debug),以下四个寄存器的值必须设置为全零(0):SBRRANGE0.sbr_address_range_mask_0SBRRANGE1.sbr_address_range_mask_1SBRSTART0.sbr_address_start_mask_0SBRSTART1.sbr_address_start_mask_1

这四个寄存器默认值为零,表示不进行地址范围的限制,或者是设置为对整个内存范围有效。

调试模式下的覆盖设置

- 如果进行调试操作,则可以通过修改

SBRSTART1和SBRSTART0寄存器来覆盖起始地址。 SBRSTART1和SBRSTART0寄存器的有效值范围是从0x0到2^n - (MSTR.burst_rdwr x 2),其中n是内存控制器的地址宽度(MEMC_HIF_ADDR_WIDTH)。这意味着起始地址可以设置为从0到一个值,具体值取决于内存控制器的地址宽度。- 地址范围的限制:

SBRRANGE1和SBRRANGE0寄存器用于设置最大地址范围,必须保证此范围不超过内存的容量。

- 如果进行调试操作,则可以通过修改

4. Inline ECC模式下的寄存器设置

受保护区域的地址配置

在Inline ECC模式下,SBR地址寄存器必须配置为受保护区域的地址范围。受保护区域的地址设置由以下几个寄存器控制:ECCCFG0.ecc_region_mapECCCFG0.ecc_region_map_granuECCCFG0.ecc_region_map_other

这些寄存器用于定义哪些内存区域是受保护的,SBR只能在这些区域内操作。

最小值和最大值的限制

SBRSTART1.sbr_address_start_mask_1和SBRSTART0.sbr_address_start_mask_0寄存器的最小值可以设置为0,但该地址必须在受保护的区域内。SBRRANGE1.sbr_address_range_mask_1和SBRRANGE0.sbr_address_range_mask_0的最大值可以设置为ECC区域的起始地址减1,但也必须在受保护的区域内。

受保护区域的说明

受保护区域的详细信息可以通过查阅手册中的“Selectable Protected Regions”(可选的受保护区域)部分了解。这些区域的配置决定了ECC Scrubber可以操作的内存范围。

NOTE

1. 地址寄存器说明

SBRSTART0.sbr_address_start_mask_0、SBRSTART1.sbr_address_start_mask_1、SBRRANGE0.sbr_address_range_mask_0、SBRRANGE1.sbr_address_range_mask_1:这些是通道0(CH0)的寄存器,用于设置SBR的起始地址和地址范围。SBRSTART0DCH1.sbr_address_start_mask_dch1_0、SBRSTART1DCH1.sbr_address_start_mask_dch1_1、SBRRANGE0DCH1.sbr_address_range_mask_dch1_0、SBRRANGE1DCH1.sbr_address_range_mask_dch1_1:这些是双通道配置中的通道1(CH1)的寄存器,作用与上述CH0寄存器相同,负责配置CH1通道上的SBR起始地址和地址范围。

2. 编程指导原则

- 对于通道0和通道1的寄存器,它们的编程原则是相同的。也就是说,在设置这些寄存器时,你需要遵循相同的规则,确保地址范围正确并且不超过内存容量。

- 特别注意通道1的内存容量:当编程通道1的寄存器时,需要特别考虑通道1的内存容量。也就是说,配置通道1的SBR寄存器时,必须确保设置的起始地址和最大地址范围在CH1的内存容量范围内,不超过其实际物理内存大小。

DDR控制器中的ECC擦除器(ECC Scrubber)在不同模式下如何生成和管理内存访问的地址

1. 地址生成机制

Sideband ECC模式

在这种模式下,ECC擦除器(SBR)会根据ADDRMAP寄存器中的设置自动计算最大地址,然后从地址0开始进行读取,直到最大地址。如果你设置了如下寄存器:

SBRSTART0.sbr_address_start_mask_0SBRSTART1.sbr_address_start_mask_1SBRRANGE0.sbr_address_range_mask_0SBRRANGE1.sbr_address_range_mask_1

如果这些寄存器被编程为非零值,ECC擦除器将从指定的起始地址开始,读取到指定的结束地址。

这些寄存器用来设置ECC擦除器的起始地址和读取范围

Inline ECC模式

- 在此模式下,ECC擦除器只能在“受保护区域”内生成地址。如果配置了没有保护的区域或ECC区域,它会跳过这些区域,不进行任何操作。

- 如果起始地址和范围掩码(由

SBRSTART和SBRRANGE寄存器配置)指向的是没有保护的区域,或者是ECC区域,ECC擦除器会跳过这些区域,直接进入下一个有效的地址。 - 如果指定的地址范围完全没有受保护区域,ECC擦除器不会生成任何命令。

- 如果起始地址和范围掩码(由

2. 特殊情况处理:

- 如果设置的地址范围(由寄存器

SBRRANGE0和SBRRANGE1定义)位于ECC区域内(例如,地址范围是2^n - 1),在快速连续的擦除读取或初始化写操作(tSCRUBI = 0)时,ECC擦除器会不断循环访问有效地址。

3. 附加说明:

- LPDDR3和LPDDR4的特殊配置:

- 当

ADDRMAP6.lpddr34_3gb_6gb_12gb寄存器配置为特定值时(例如,LPDDR3或LPDDR4的某些配置),写请求或读取修改写(RMW)请求会被丢弃,且会触发hif_wdata_ptr_addr_err或hif_rdata_addr_err错误信号。 - 对于读取请求(即使行地址是无效的2’b11),控制器会执行虚拟读取,将地址行的前两位从2’b11改为2’b10,返回的读数据会被掩码为零。

- 在此情况下,ECC擦除器不会发送无效地址的事务,而是跳过该地址,继续访问下一个有效地址。

- 当

4. LPDDR3/LPDDR4地址有效性

- 寄存器

SBRRANGE0、SBRRANGE1、SBRSTART0、SBRSTART1必须设置为有效的LPDDR3或LPDDR4地址。如果这些寄存器设置为无效地址,ECC擦除器会跳过无效地址并向下一个有效地址发起命令。

5. SDRAM和MRAM混合配置:

- 在SDRAM和MRAM混合配置下,如果ECC擦除器对保留的内存区域执行读或写操作,地址映射器会忽略HIF地址的高位,只考虑MRAM大小所需的地址位。这会导致地址别名现象,也就是说,MRAM地址可能会被多次访问,虽然这不会引起功能上的问题,但会导致一些性能问题,具体表现为重复访问某些地址。

ECC擦除器(ECC Scrubber)在不同配置下的状态(Status)管理

1. SBRCTL.scrub_interval寄存器

SBRCTL.scrub_interval是控制擦除间隔的寄存器。它指定了擦除命令发出的时间间隔。- 如果

SBRCTL.scrub_interval设置为非零值,并且有正在执行的读取命令,则系统会设置SBRSTAT.scrub_busy为1,表示擦除操作仍在进行中,**同时不会设置SBRSTAT.scrub_done**(表示擦除还没有完成)。

2. scrub_interval为0时的行为

当 SBRCTL.scrub_interval 设置为 0 时,ECC擦除器的行为如下:

读取操作(Reads)

- 如果

scrub_interval设置为 0,ECC擦除器将持续发出读取命令,并不会在地址范围被完全覆盖后自动停止。在第一个循环结束后,擦除器会继续工作,系统的状态会显示:SBRSTAT.scrub_done = 1,表示擦除已完成(但并没有停止擦除操作),SBRSTAT.scrub_busy = 1,表示擦除操作仍然在进行中。

写入操作(Writes)

如果是写入命令,ECC擦除器将在完整的地址范围覆盖后停止发出写入命令

。在第一个循环结束后,擦除器会停止,系统状态将会显示:

SBRSTAT.scrub_done = 1,表示擦除已完成,SBRSTAT.scrub_busy = 0,表示擦除操作已经完成且不再忙碌。

3. Inline ECC模式下的特殊情况

在Inline ECC模式下,寄存器配置和擦除器行为会有一些额外的特殊规则:

无保护区域和ECC区域的影响

- 如果配置了无保护区域或ECC区域(即设置了

SBRRANGE1、SBRRANGE0寄存器中的地址范围掩码为无保护区域或ECC区域),并且SBRCTL.scrub_interval设置为0,那么在读取或写入过程中,ECC擦除器不会生成SBRSTAT.scrub_done状态,这意味着它不会自动报告操作完成。

无保护区域的不可预测行为

- 如果

SBRSTART或SBRRANGE寄存器配置的地址范围指向的是无保护区域,那么uMCTL2(内存控制器)将会表现出不可预测的行为。即,它无法确保擦除操作正常执行。

关于ECC区域的行为

- 如果

SBRRANGE1和SBRRANGE0寄存器的配置设置为2^n - 1,其中n是内存地址宽度(MEMC_HIF_ADDR_WIDTH),那么这个地址位于ECC区域。在这种情况下,即使执行的是连续的擦除读取或初始化写操作,ECC擦除器也不会生成SBRSTAT.scrub_done信号。

ECC擦除器(SBR)在不同低功耗模式下的行为

1. 硬件控制的低功耗操作(Low Power Operation - Hardware Controlled)

在硬件控制的低功耗模式下,**uMCTL2(内存控制器)**会根据硬件的自动控制来决定何时进入低功耗模式,且在这种模式下**ECC擦除器(SBR)会自动工作**,无需软件干预。这个行为可以通过设置SBRCTL.scrub_during_lowpower为‘0’来禁用。

低功耗模式类型

自动触发的低功耗模式

- 当控制器进入低功耗模式(如

STAT.operating_mode的值为10(power-down模式)或11(自刷新模式))时,SBR会自动发出擦除命令。 - 如果在自刷新模式(

STAT.selfref_type设置为11)下,SBR的擦除命令会自动唤醒控制器,使其从低功耗模式中恢复过来。 - 在低功耗模式下,擦除命令的数量是由寄存器

SBRCTL.scrub_burst[2:0]指定的(最大可设置为1024),它控制了每次发出的连续擦除命令数量。这些命令的间隔是scrub_burst * scrub_interval周期。 - 需要注意的是,SBR不能将SDRAM重新置于低功耗状态,如果没有进一步的空闲状态,控制器会重新进入低功耗模式。

- 当控制器进入低功耗模式(如

硬件低功耗接口触发的低功耗模式

- 该模式通过硬件低功耗接口来触发。如果控制器进入低功耗模式,必须通过相同的接口来退出。

- 如果

SBRCTL.scrub_during_lowpower为‘1’,则每隔scrub_burst * scrub_interval周期,SBR会尝试发出scrub_burst数量的擦除命令。 - 这种模式依赖于

cactive_in_ddrc信号,该信号会触发cactive_ddrc输出信号。当cactive_ddrc信号被拉高时,SBR会触发控制器退出低功耗模式。

2. 软件控制的低功耗操作(Low Power Operation - Software Controlled)

当uMCTL2进入软件控制的低功耗模式(例如自刷新、深度功耗关断(DPD)或最大节能模式(MPSM))时,SBR的操作就需要由软件来管理。以下是操作步骤和建议:

操作步骤

- 在进入低功耗模式前禁用SBR:

- 在进入任何软件控制的低功耗模式之前,软件应该通过将

SBRCTL.scrub_en设置为‘0’来禁用SBR。这样可以防止在低功耗模式下SBR继续工作。

- 在进入任何软件控制的低功耗模式之前,软件应该通过将

- 低功耗模式下执行擦除操作:

- 如果在低功耗模式下需要执行擦除操作,软件可以通过连续发出擦除读取命令(back-to-back scrub read commands)来迅速完成对整个地址范围的擦除。

- 唤醒uMCTL2和初始化SDRAM/PHY:

- 在低功耗模式下,如果需要继续执行擦除操作,软件首先需要唤醒uMCTL2,并在必要时重新初始化SDRAM和PHY(物理层接口)。

- 加速SBR擦除:

- 如果需要以更高速度启动SBR操作,软件可以将

scrub_interval设置为0,并启用SBR,从而加速擦除操作。

- 如果需要以更高速度启动SBR操作,软件可以将

- 完成擦除后的通知:

- 一旦SBR完成整个SDRAM范围的擦除,它会通过中断信号(

sbr_done_intr)通知软件,此外,SBRSTAT.scrub_done状态位也会被设置,软件可以轮询该状态位。 - 如果

scrub_interval设置为0,且SBR正在正常工作,sbr_done_intr和scrub_done状态位永远不会被设置为“完成”状态。

- 一旦SBR完成整个SDRAM范围的擦除,它会通过中断信号(

- 继续或停止擦除操作:

- 如果软件不想等待完整的擦除操作完成,可以随时将

scrub_interval设置为非零值,SBR会从开始地址重新启动擦除命令。 - 如果需要停止擦除操作或恢复正常操作,可以禁用SBR或将

scrub_interval设置回正常的工作值(大于0),这将清除中断信号和状态位。

- 如果软件不想等待完整的擦除操作完成,可以随时将

ECC擦除器(SBR)的初始化写操作过程

1. SBR初始化模式(Initialization Writes)

SBR(Scrubber)模块不仅用于擦除操作,还可以用来初始化内存中的数据。通过设置SBRCTL.scrub_mode寄存器为1,SBR就可以启动初始化写操作。这个模式下,SBR会向内存写入一个定义的模式或数据。

- SBRCTL.scrub_mode:此寄存器需要设置为

1,以启用初始化写操作。 - SBRWDATA0 和 SBRWDATA1:如果内存的数据宽度(

MEMC_DRAM_DATA_WIDTH)为64位,可以通过这两个寄存器设置要写入的模式数据。

2. 内存保护区域配置

在内联ECC模式(Inline ECC)下,初始化写操作必须确保写入的数据范围是受保护的。内存中某些区域是“受保护区域”,这些区域需要确保ECC数据的正确性。

- SBRSTART1 和 SBRSTART0:这两个寄存器定义了初始化写操作的起始地址掩码,必须设置在ECC保护区域内。

- SBRRANGE1 和 SBRRANGE0:这两个寄存器定义了初始化操作的地址范围掩码,也需要设置在ECC保护区域内。

保护区域的定义取决于ECC配置寄存器,例如:

ECCCFG0.ecc_region_map、ECCCFG0.ecc_region_map_granu和ECCCFG0.ecc_region_map_other等,这些寄存器定义了保护区域的映射方式。

受保护区域的地址范围:

- 最小值:

SBRSTART寄存器的最小值为0,只要该地址位于保护区域内。 - 最大值:

SBRRANGE寄存器的最大值为ECC区域起始地址 - 1,也必须在保护区域内。

如果使用侧带ECC模式(Sideband ECC),则上述寄存器(SBRSTART和SBRRANGE)可以保留默认值。

3. 初始化步骤

在PHY和SDRAM初始化完成后,以下步骤应该按照顺序进行,以完成内存的初始化写操作:

- 如果启用了内联ECC模式(

MEMC_INLINE_ECC定义并启用内联ECC模式),则设置ECCCFG1.ecc_region_parity_lock为1,锁定ECC区域的奇偶校验。 - 关闭AXI端口:通过设置

PCTRL_n.port_en为0,阻止AXI端口进行任何事务。 - 如果启用了片上ECC(

UMCTL2_OCECC_EN定义并且OCECCCFG0.ocecc_en为1),则将OCECCCFG0.ocecc_en设置为0,以避免在初始化期间触发ECC错误中断。 - 启用初始化写操作:将

SBRCTL.scrub_mode设置为1,启用SBR的初始化写模式。 - 设置擦除间隔:将

SBRCTL.scrub_interval设置为0,表示不需要间隔时间。 - 设置要写入的模式数据:通过

SBRWDATA0和SBRWDATA1寄存器设置要写入的模式数据。 - 启用SBR:通过设置

SBRCTL.scrub_en为1,启动SBR操作。 - 轮询完成标志:通过轮询

SBRSTAT.scrub_done来判断所有写命令是否已发送完成(值为1表示完成)。 - 确认SBR完成:轮询

SBRSTAT.scrub_busy,确保所有写数据已发送完成(值为0表示完成)。 - 禁用SBR:通过将

SBRCTL.scrub_en设置为0来禁用SBR。 - 如果启用了片上ECC,重新启用片上ECC:通过设置

OCECCCFG0.ocecc_en为1。 - 准备正常的擦除操作:将

SBRCTL.scrub_mode设置为0,表示恢复到正常的擦除读取模式,并根据SBRCTL.scrub_interval设置擦除间隔时间(tSCRUBI)。 - 启用SBR:通过将

SBRCTL.scrub_en设置为1,启动正常的SBR操作。 - 启用AXI端口:通过将

PCTRL_n.port_en设置为1,重新启用AXI端口进行正常事务操作。

4. 注意事项

- 在进入读取模式(Read mode)之前,必须确保内存中已经存在有效的数据和ECC数据。因此,初始化写操作必须先进行,以确保内存中存有有效的ECC数据。

2.39.6.3 DDR控制器在测试模式(Test Mode)下的行为

1. 测试模式(Test Mode)

通过启用ECCCFG0.test_mode(该寄存器在UMCTL2_REGS Registers中定义),可以获得对ECC字节(byte 8)的读写访问。在此模式下,能够通过HIF(High-Speed Interface)信号进行ECC字节的数据传输。

- 写入数据和掩码:在测试模式下,您可以通过HIF信号

hif_wdata_ecc写入数据,并通过信号hif_wdata_mask_ecc指定掩码来应用这些数据。 - 读取数据:通过HIF信号

hif_rdata_ecc,您可以读取ECC字节的数据。

测试模式的使用限制

- 总线宽度要求:测试模式仅支持全宽总线控制器。具体来说,当

ECCCFG0.test_mode设置为1时,MSTR.bus_width必须设置为0。这意味着总线宽度必须为64位,即不支持较低宽度的总线。 - 频率配置:如果

MEMC_PROG_FREQ_RATIO设置为1,那么MSTR.frequency_ratio也必须设置为0。 - HIF接口配置:如果uMCTL2配置为使用HIF接口(

UMCTL2_INCL_ARB = 0),则才可以启用测试模式。

交易类型的限制

启用test_mode时,只有读写交易(Read/Write transactions)被允许,而读改写(RMW,Read-Modify-Write)交易是不允许的。这是为了确保ECC字节的操作简单明了,避免由于读改写操作导致不必要的复杂行为。

忽略ECC模式

当ECCCFG0.test_mode设置为1时,ECCCFG0.ecc_mode的值会被忽略,表示不需要考虑ECC的工作模式。

2. 具有可修正错误和不可修正错误的控制器行为

这部分描述了在内联ECC模式(Inline ECC)**和**侧带ECC模式(Sideband ECC)**下,当发生同时包含**可修正错误和不可修正错误的情况时,控制器如何处理这些错误。

内联ECC模式(Inline ECC)

- 多通道同时发生错误:如果Scrubber周期性读取操作(通常是为保证内存健康的读操作)在多个信道(Lanes)上检测到可修正错误和不可修正错误,控制器会采取以下措施:

- 控制器会生成一个**修正写入(RMW)**命令,针对可修正错误进行纠正。这意味着,对于**可修正错误**,它会修改数据,恢复到正确状态。

- 对于不可修正错误,控制器不会修正数据,而是通过损坏ECC来保留错误数据。也就是说,ECC的校验值将被破坏,但数据本身不会被修正,系统会保持该不可修正错误。

侧带ECC模式(Sideband ECC)

- 在侧带ECC模式下,如果在读取操作中发生了多个通道上同时有可修正和不可修正的错误,控制器不会生成修正命令。换句话说,控制器不会对该地址执行任何修复操作,不管数据是否可以修正,只会保持不可修正错误的状态。

2.39.7 ECC数据污染(ECC Data Poisoning)

1. ECC数据污染的概述

ECC数据污染功能允许在写入的数据中注入可修正(1位)或不可修正(2位)ECC错误。然后可以通过读取这些数据来检查系统如何处理这些错误。这个功能常用于测试系统的ECC错误检测和处理机制。

2. 启用ECC数据污染

要启用ECC数据污染,必须做以下几件事:

- 设置

ECCCFG1.data_poison_en寄存器位为1。这个寄存器控制是否启用ECC数据污染功能。 - 设置目标地址寄存器(如ECCPOISONADDR0和ECCPOISONADDR1),这些寄存器定义了目标地址(包括rank、bank、row和column),即在哪个内存位置注入ECC错误。

3. 选择ECC错误类型

ECCCFG1.data_poison_bit字段控制注入的错误类型:- 如果

data_poison_bit设置为0,则注入不可修正(2-bit)ECC错误。 - 如果

data_poison_bit设置为1,则注入可修正(1-bit)ECC错误。

- 如果

4. ECC数据污染的实现

每当uMCTL2检测到对某个目标地址的HIF写操作或RMW(读修改写)操作时,它会对该地址的ECC字节的最低有效1位或2位进行反转,然后将数据写入SDRAM中。具体来说:

- 写操作:在写入数据时,ECC字节的最低有效位(1或2位)会被反转。

- 读操作:当该地址的数据被读取时,uMCTL2会检测到发生了可修正或不可修正错误,并通过中断和ECC报告寄存器进行标记。

5. 列地址对齐要求

为确保数据污染正确插入,列地址(ecc_poison_col)需要与SDRAM的burst对齐。根据MEMC_BURST_LENGTH(SDRAM突发长度),你需要设置列地址的某些位为0,具体如下:

- MEMC_BURST_LENGTH = 8:

- 全宽总线:设置

ecc_poison_col[2:0]为0。 - 半宽总线:设置

ecc_poison_col[3:0]为0。 - 四分之一宽总线:设置

ecc_poison_col[4:0]为0。

- 全宽总线:设置

- MEMC_BURST_LENGTH = 4:

- 全宽总线:设置

ecc_poison_col[1:0]为0。 - 半宽总线:设置

ecc_poison_col[2:0]为0。 - 四分之一宽总线:设置

ecc_poison_col[3:0]为0。

- 全宽总线:设置

- MEMC_BURST_LENGTH = 16:

- 全宽总线:设置

ecc_poison_col[3:0]为0。 - 半宽总线:设置

ecc_poison_col[4:0]为0。 - 四分之一宽总线:设置

ecc_poison_col[5:0]为0。

- 全宽总线:设置

6. ECC错误注入时机

- 错误是在SDRAM数据突发的第一数据节拍(data beat)时插入的,并且必须与列地址对齐。

7. 禁用测试模式

如果启用了ECC数据污染(ECCCFG1.data_poison_en = 1),则必须禁用测试模式(ECCCFG0.test_mode = 0)。这意味着在启用ECC数据污染时,不能同时启用测试模式。

8. 与“芯片内奇偶校验错误”(On-chip Parity Error)交互

- 如果发生芯片内奇偶校验错误(On-chip Parity Error),无论

ECCCFG1.data_poison_bit字段的设置如何,ECC字节的最低有效2位始终会被反转。 - 当发生芯片内奇偶校验错误时,写数据路径上的ECC字节最低2位始终反转,这会导致ECC字节的损坏。

9. 禁用OCPAR写数据奇偶校验污染

如果启用了ECC数据污染功能,那么OCPAR写数据奇偶校验污染必须被禁用,并且确保在ECC数据污染过程中不会发生OCPAR写数据奇偶校验错误。否则,ECC数据污染的功能可能无法正常工作,无法观察到预期的行为。

2.39.8-10见手册

本文链接: https://talent-tudou.github.io/2024/12/13/DDR/uMCTL2-ECC Support/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!